1

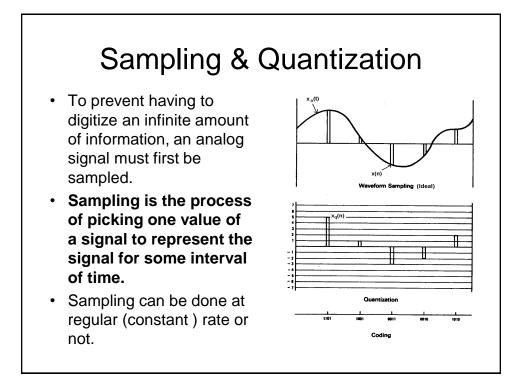

# Sampling

- Sampling is done by a circuit called a *sample-and-hold* (*S/H*), which, at a sampling instant, transfers the input signal to the output and holds it steady, even though the input signal may still be changing.

- Most modern ADC chip has a built-in S/H or T/H, and virtually all data acquisition systems include them.

- Of course, sampling necessarily throws away some information, so the art of sampling is in choosing the right sample rate so that enough of the input signal is preserved.

#### Minimum sampling rate (Nyquest Rate)

• Nyquest criterion states that the sampling rate must be at least twice the highest frequency of the signal of interest:

#### fsampling > 2f signal

- Nyquest criterion guarantees the preservation of the frequency content of the signal, but not the time dependency

- In order to be able to reconstruct the signal in time domain, as a rule of thump , we use : fsampling > 10 f signal

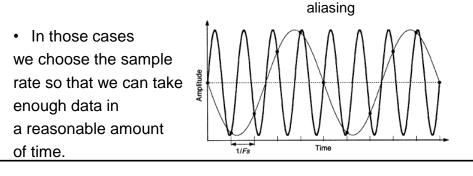

- Aliasing occurs when the sampling is done at a rate less than Nyquest rate

- Sample rates are specified in samples/s, or S/s, and it is also common to specify rates in kS/s, MS/s, and even GS/s.

## Minimum sampling rate (Nyquest Rate)

- Sample rates are specified in samples/s, or S/s, and it is also common to specify rates in kS/s, MS/s, and even GS/s.

- It is not always necessary to worry about aliasing.

- When an instrument is measuring slow-moving dc signals or is gathering data for statistical analysis, for instance, getting frequencies right is not important.

### Antialias Filter

- On the other hand, if the instrument is a spectrum analyzer, where frequency does matter, or an oscilloscope, where fine time detail is needed, aliasing certainly is an issue.

- When aliased signals from beyond the frequency band of interest can interfere with measurement, an instrument needs to have an *anti-alias filter* before the S/H.

- An anti-alias filter is a low-pass filter with a gain of 1 throughout most of the frequency band of interest.

- As frequency increases, it begins to attenuate the signal; by the Nyquist frequency it must have enough attenuation to prevent higher-frequency signals from reaching the S/H with enough amplitude to disturb measurements.

# Antialias Filter

- An efficient antialias filter must attenuate rapidly with frequency in order to make most of the baseband usable.

- Popular analog filters with rapid cutoff include elliptic and Chebyshev filters, which use zeros to achieve fast cutoff, and Butterworth filters (sixth order and above), which do not attenuate as aggressively, but have very flat passband response.

- Some ADCs do not need a S/H at all.

- If the ADC is converting a slow-moving or dc signal and precise timing isn't needed, the input may be stable enough during conversion that it is as good as sampled.

- There are also *integrating ADCs* (discussed later), which average the input signal over a period of time rather than sampling it.

- However, internally they actually sample the average.

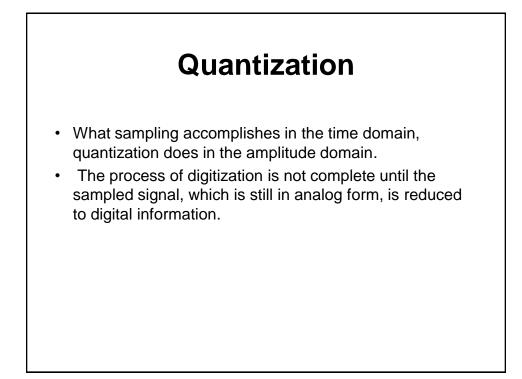

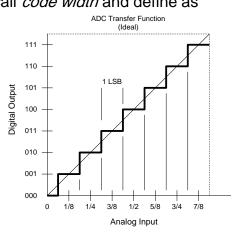

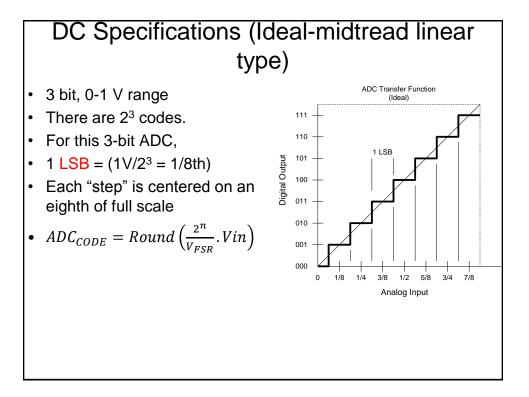

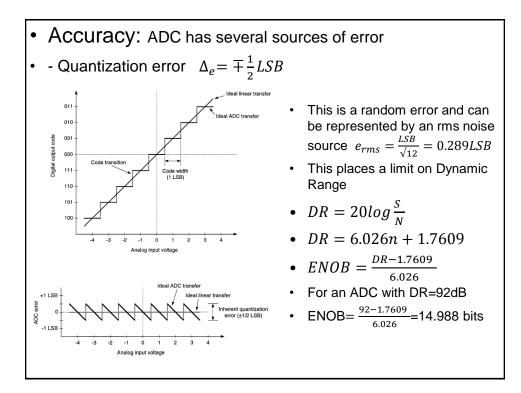

- Figure represents a three-bit quantizer, which maps a continuum of analog input values to only eight (2<sup>3</sup>) possible output values.

- Each step in the staircase has (ideally) the same width along the *x*-axis, which we call *code width* and define as 1*LSB (least significant bit)*

- In this case 1 LSB is equal to 1/8 V. Each digital code corresponds to one of eight 1-LSB intervals making up the analog input range, which is 8 LSB (and also 1 V in this case).

- 1. Range: The input range of ADC is the span of voltage over which the ADC can make conversion

- The end points at the bottom and the top of the range are called -*full-scale* and + *full-scale*, respectively.

- When --full-scale = 0 V the range is called unipolar

- when -full-scale is a negative voltage of the same magnitude as +full-scale the range is said to be *bipolar*

- When the input voltage exceeds the input range, the conversion data are certain to be wrong, and most ADCs report the code at the end point of the range closest to the input voltage.

- > This condition is called an overrange

•

$$\Delta = LSB = Q = \frac{V_{FSR}}{2^n}$$

$$\Delta = LSB = Q = \frac{2.5}{2^8} = \frac{2500mV}{256} = 9.765 \text{ mV}$$

Or as %

$$\Delta = \frac{9.765}{2500} * 100\% = 0.3906\%$$

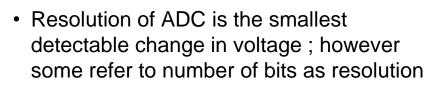

#### ADC Resolution vs. Quantization Parameters

| Resolution,<br>Bits (n) | 2 <sup>n</sup> | LSB, mV<br>(2.5V FS) | %<br>Full Scale | ppm<br>Full Scale | dB<br>Full Scale |

|-------------------------|----------------|----------------------|-----------------|-------------------|------------------|

| 8                       | 256            | 9.77                 | 0.391           | 3906              | -48.0            |

| 10                      | 1024           | 2.44                 | 0.098           | 977               | -60.0            |

| 12                      | 4096           | 0.610                | 0.024           | 244               | -72.0            |

| 14                      | 16,384         | 0.153                | 0.006           | 61                | -84.0            |

| 16                      | 65,536         | 0.038                | 0.0015          | 15                | -96.0            |

| 18                      | 262,164        | 0.0095               | 0.00038         | 3.8               | -108.0           |

| • Highe                 | er n giv       | es bette             | er resol        | ution             |                  |

#### **Example** • Given a sensor with 0.02 V / degree C sensitivity, choose an a suitable size ADC with VFSR=2V such that to be able to measure 0-100 deg C with : a) 1 deg C resolution b) 0.1 deg C resolution • **Solution:** • A) 1 deg C => 0.02 V • 100 deg C => 100x 0.02=2V • We have an ADC with VFSR= 2 V range • For 1 deg C resolution, ADC resolution $\Delta = 0.02$ V • $\Delta = 0.02V = \frac{V_{FSR}}{2^n} = \frac{2}{2^n} = \Rightarrow 2^n = 100 = \Rightarrow n = \log_2(100) = 6.644$ • N must be an integer, so we choose n=7

#### Example

- B) For 0.1 deg C resolution , ADC resolution  $\Delta$  = 0.002 V

- $\Delta = 0.002V = \frac{V_{FSR}}{2^n} = \frac{2}{2^n} \Longrightarrow 2^n = 1000 \Longrightarrow n = \log_2(1000) \Longrightarrow 9.97$

- N must be an integer, so we choose n=10

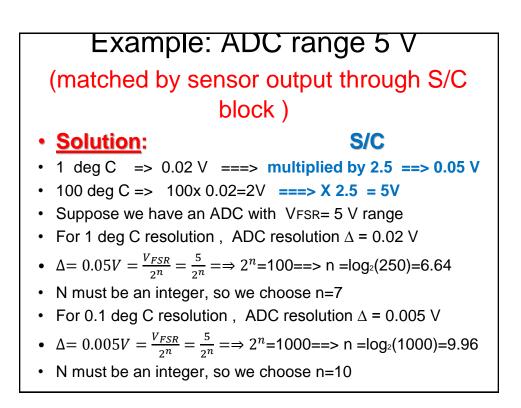

#### In this example, the sensor output is matched to ADC input

(not matched by sensor output "2V")

- Solution:

- 1 deg C => 0.02 V

- 100 deg C => 100x 0.02=2V

- Suppose we have an ADC with VFSR= 5 V range

- + For 1 deg C resolution , ADC resolution  $\Delta$  = 0.02 V

•

$$\Delta = 0.02V = \frac{V_{FSR}}{2^n} = \frac{5}{2^n} \Longrightarrow 2^n = 250 \Longrightarrow n = \log_2(250) = 7.96$$

- N must be an integer, so we choose n=8

- For 0.1 deg C resolution , ADC resolution  $\Delta$  = 0.002 V

•

$$\Delta = 0.002V = \frac{V_{FSR}}{2n} = \frac{5}{2n} \Longrightarrow 2^n = 2500 \Longrightarrow n = \log_2(2500) = 11.3$$

• N must be an integer, so we choose n=12

•

# Conclusion about range matching

- When the ranges are not matched, higher number of bits "n" is required to achieve higher measurement resolution

- When we match the output range of the sensor to the input range of ADC, we can get better resolution of a given ADC with given number of bits

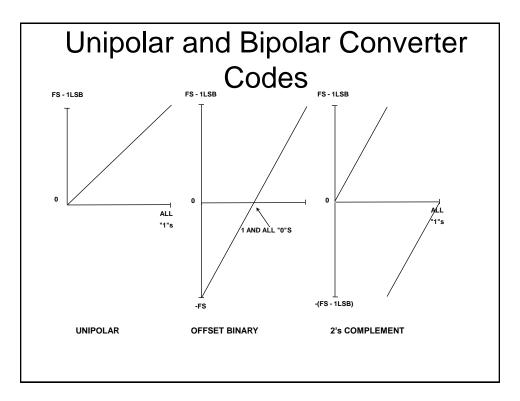

# **Coding Conventions**

- There are several different formats for ADC output data:

- Unipolar

- Bipolar

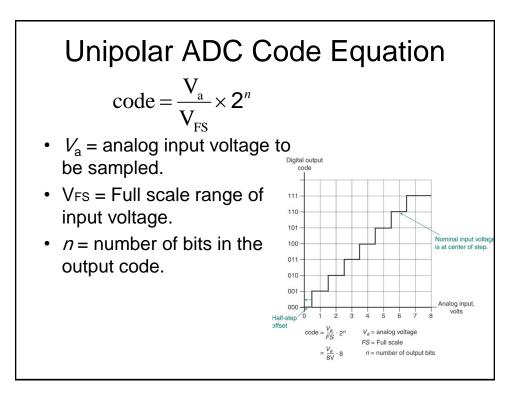

- An ADC using *binary* coding produces all 0s (e.g., 000 for the three-bit converter) at –full-scale and all 1s (e.g., 111) at +full-scale.

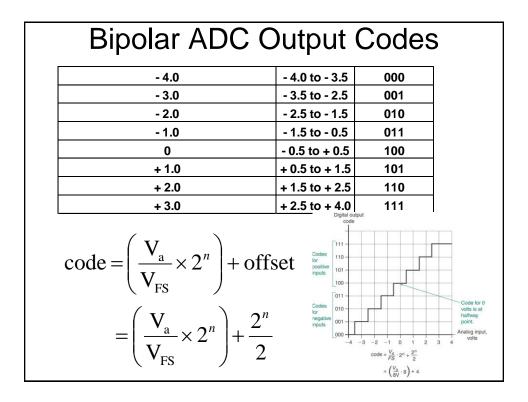

- If the range is bipolar, so that –full-scale is a negative voltage, binary coding is sometimes called *offset binary* since the code 0 does not refer to 0 V.

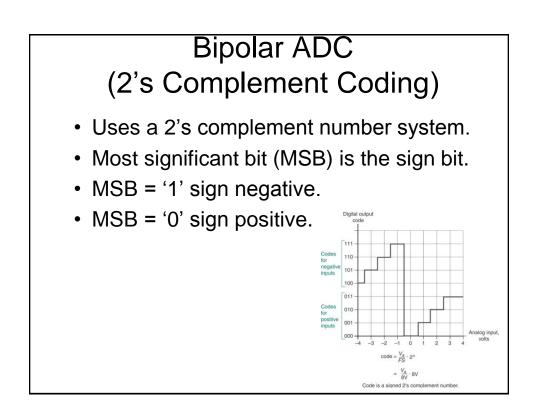

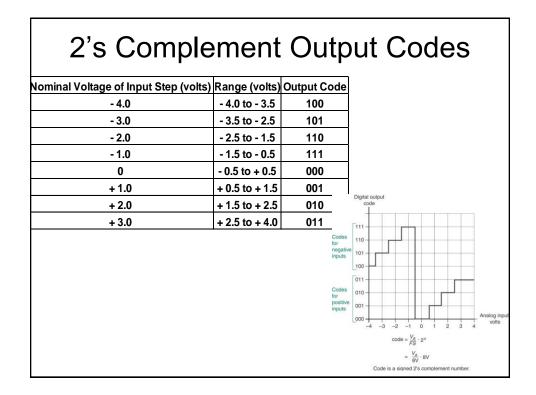

- To make digital 0 correspond to 0 V, bipolar ADCs use *two's* complement coding, which is identical to offset binary coding except that the most significant bit (MSB) is inverted, so that 100 ... 00 corresponds to –full-scale, 000 ... 00 corresponds to 0 V (*midscale*), and 011 ... 11 corresponds to +full-scale.

#### **Coding Conventions-BCD**

- Decimal-digit ADCs, such as those used in digital voltmeters, use a coding scheme call *binary-coded decimal (BCD)*

- BCD data consists of a string of four-bit groups of binary digits.

- Each four-bit group represents a decimal digit, where 0000 is 0, 0001 is 1, and so on, up to 1001 for 9.

- The other six combinations (1010 through 1111) are invalid, or can be used for special information, such as the sign of the conversion.

| Unipolar ADC                          | Outpu         | ut Code     | es                                                                         |

|---------------------------------------|---------------|-------------|----------------------------------------------------------------------------|

| Nominal Voltage of Input Step (volts) | Range (volts) | Output Code |                                                                            |

| 0.0                                   | 0.0 - 0.5     | 000         |                                                                            |

| 1.0                                   | 0.5 - 1.5     | 001         |                                                                            |

| 2.0                                   | 1.5 - 2.5     | 010         |                                                                            |

| 3.0                                   | 2.5 - 3.5     | 011         |                                                                            |

| 4.0                                   | 3.5 - 4.5     | 100         |                                                                            |

| 5.0                                   | 4.5 - 5.5     | 101         |                                                                            |

| 6.0                                   | 5.5 - 6.5     | 110         |                                                                            |

| 7.0                                   | 6.5 - 8.0     | 111         |                                                                            |

| $code = \frac{V_a}{V_{FS}} \times 2'$ | 1             | offset      | Nominal reput voltage<br>is at center of step.<br>5 6 7 6 voltas<br>voltas |

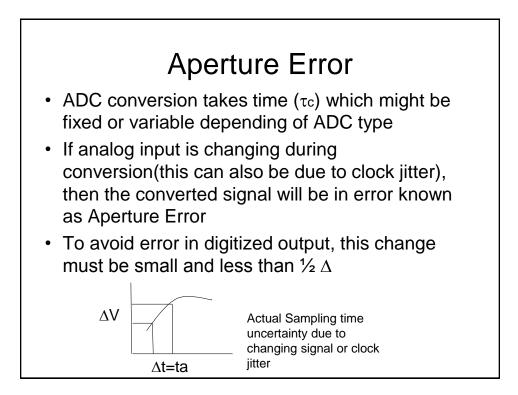

#### **Aperture Errors**

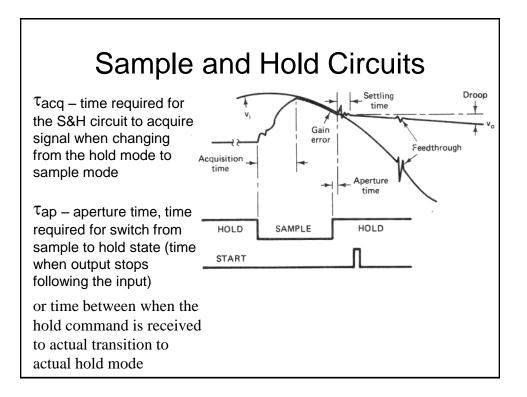

- Aperture errors have to do with the **timing of** analog-to-digital conversions, particularly of the S/H.

- Aperture delay characterizes the amount of time that lapses from when an ADC (S/H) receives a convert pulse to when the sample is held as a result of the pulse.

• Assume Vin=Vref Sin  $\omega$ ot

•

$$\left(\frac{\Delta V}{\Delta t}\right)_{max} = V_{REF}\omega_0 \implies \Delta t = \frac{\Delta V}{V_{REF}\omega_0}$$

$let \ \Delta V = \frac{1}{2}LSB = \frac{V_{REF}}{2.2^n}$

$\Delta t = \frac{\frac{V_{REF}}{2.2^n}}{V_{REF}\omega_0} = \frac{1}{2.2^n\omega_0}$

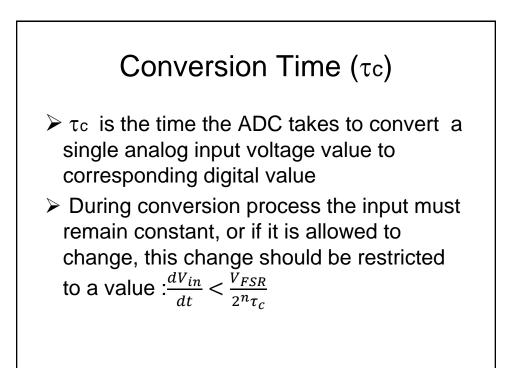

One must make sure that conversion time  $\tau_c$  is less than ta

Example: a 10 bit ADC with τc=20 µs, what is the maximum allowable rate of change (frequency) of a sinusoidal input voltage to be converted using this ADC

• Solution:

$$\frac{dV_{in}}{dt} < \frac{V_{FSR}}{2^n \tau_c}$$

$$A\omega_o < \frac{\tau_{FSR}}{2^n \tau_c}$$

, let  $A = V_{FSR}$

$\omega_o < \frac{1}{2^n \tau_c}$

$$f_o < \frac{1}{2\pi . 2^{10} 20\mu s} = 7.75 \ Hz$$

This is the maximum frequency of input to be used with this ADC>>>> If higher frequency needed , increase n or reduce  $\tau_c$

# Sample and Hold (S& H) reduces ∆t S&H is placed at the input of ADC, it holds the input signal at a constant level during conversion S&H is used to avoid errors if variations of the measurand were allowed to pass to the ADC Reduce uncertainty error in the converted output when input changes are fast compared to the conversion time Sample mode: output follows input Hold: Output is held constant until sample mode is resumed

### Commercially Available S/H

| Device<br>type | Manufacturers                                               | Acquisition<br>time            | Aperature<br>time | Settling<br>time | Features                                              | Price<br>(100s) |

|----------------|-------------------------------------------------------------|--------------------------------|-------------------|------------------|-------------------------------------------------------|-----------------|

| AD582          | Analog<br>Devices                                           | 6 μs to 0.1%<br>25 μs to 0.01% | 150 ns            | 0.5 µs           | Monolithic,<br>general purpose                        | \$ 8            |

| AD583          | Analog<br>Devices                                           | 4 μs to 0.1%<br>5 μs to 0.01%  | 50 ns             |                  | Monolithic,<br>faster                                 | 16              |

| LF398          | National                                                    | 4 μs to 0.1%<br>6 μs to 0.01%  | 150 ns            | 0.8 µs           | Monolithic,<br>general purpose                        | 3               |

| SHC298         | Burr-<br>Brown                                              | 9 μs to 0.1%<br>10 μs to 0.01% | 200 ns            | 1.5 µs           | Monolithic,<br>general purpose                        | 7               |

| AD346          | Analog<br>Devices                                           | 2 µs to 0.01%                  | 60 ns             | 0.5 µs           | Hybrid, internal<br>hold capacitor                    |                 |

| SHC85          | Analog<br>Devices,<br>Datel-<br>Intersil,<br>Burr-<br>Brown | 4 µs to 0.01%                  | 25 ns             | 0.5 µs           | Hybrid, internal<br>hold capacitor,<br>low droop rate | 70              |

| HTS0025        | Analog<br>Devices                                           | 20 ns to 0.01%                 | 20 ns             | 30 ns            | Hybrid, very fast                                     | 187             |

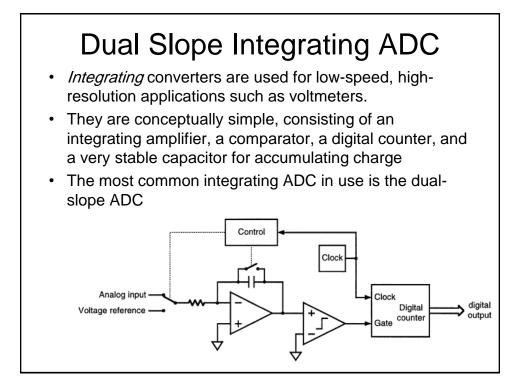

# TYPES of ADC Flash Integrating SAR Sigma-Delta

- Most ADC types have the following two blocks in common:

- Comparator ==> Vo= logic "1" if V(+) > V(-)

Vo= logic "0" if

$$V(+) < V(-)$$

· Precise and stable voltage reference

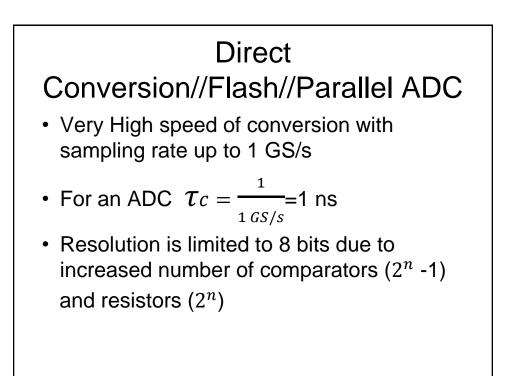

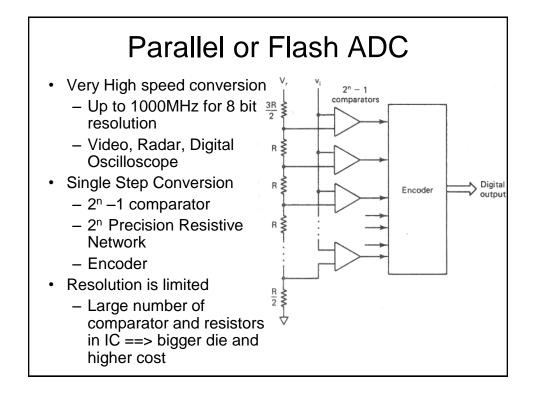

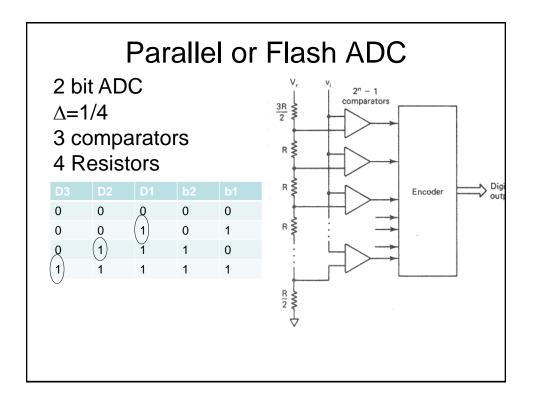

#### Flash ADC

- highest speed

- large # of comparators

- large size

- large power consumption

- 8-bit maximum resolution

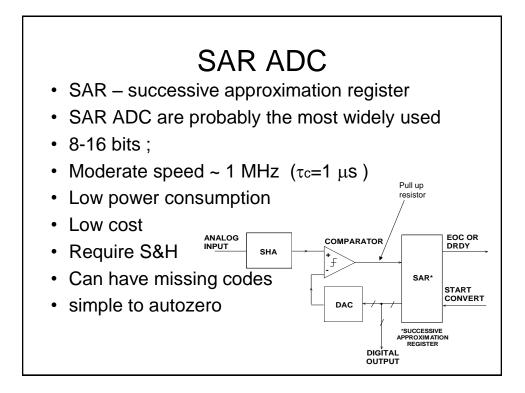

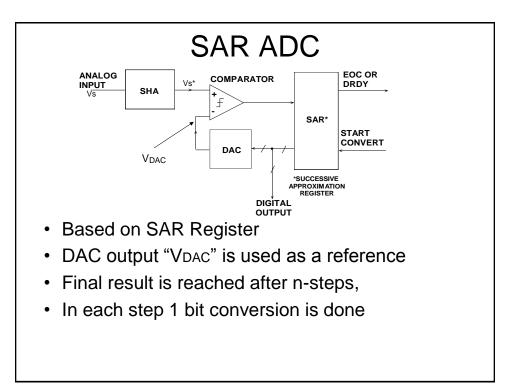

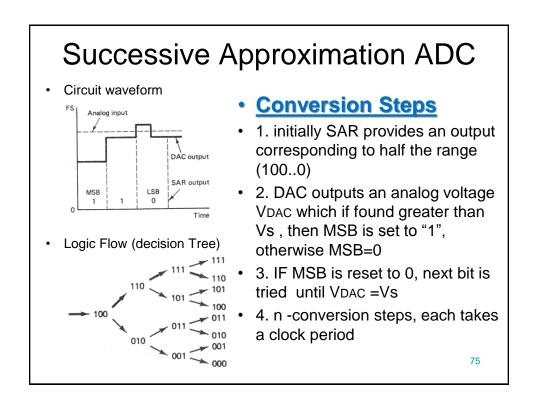

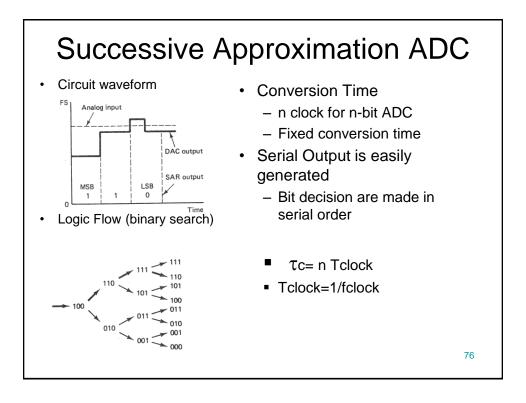

## How a Successive Approximation A/D Converter Works

- Rising/Falling Edge of Convert Start Pulse Resets Logic

- Falling/Rising Edge Begins Conversion Process

- Bit Comparisons Made on Each Clock Edge

- Conversion Time Equals Number of Comparisons

(Resolution) Times Clock Period

- The Accuracy of Conversion Depends on the DAC Linearity and Comparator Noise

#### **Successive Approximation ADC**

#### Advantages to SAR A/D converters

Low Power (12-bit/1.5 MSPS ADC: 1.7 mW)

Higher resolutions (16-bit/1 MSPS)

- Small Die Area and Low Cost

- No pipeline delay

#### Tradeoffs to SAR A/D converters

Lower sampling rates

#### **Typical Applications**

- Instrumentation

- Industrial control

- Data acquisition

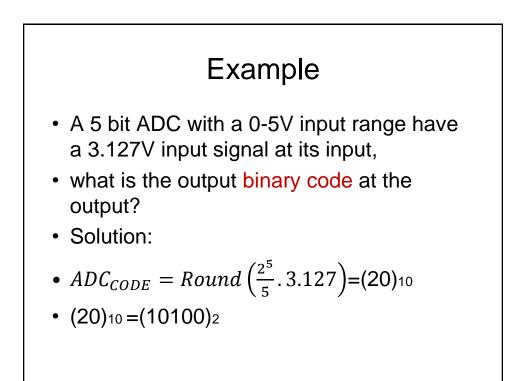

#### Example

- VFSR=5V, 4 bit, SAR ADC, Vs=Vin=3.127 V, explain how conversion . Check VDAC > Vs ? (3.75 > is done?

- Solution:

- Suppose Output is b1b2b3b4

- (1) let b1=1, b2=b3=b4=0

- 1000 ==> VDAC=8/2^4\*VREF=2.5V

- Check VDAC > Vs ? (2.5 > 3.127? ==> NO ==> set **b1=1**

- (2) set b2=1, b3=b4=0

- 1100 ==>VDAC=10/2^4\*VREF=3.75V

- 3.127? ==> Yes ==> Reset b2=0

- (3) set b3=1, b4=0

- 1010 ==> VDAC=9/2^4\*VREF=3.1255V

- Check VDAC > Vs ? (3.125 > 3.127? ==> No ==> set b3=1

- (4) set b4=1, 1011 ==> VDAC=11/2^4\*VREF=3.4375V

- Check VDAC > Vs ? (3.4375 > 3.127? ==> Yes ==> Reset **b4=0**

- Final Result: 1010

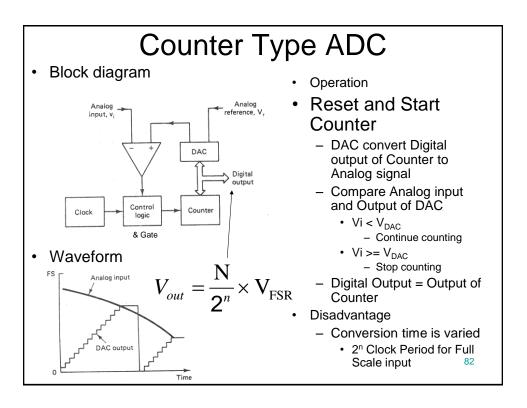

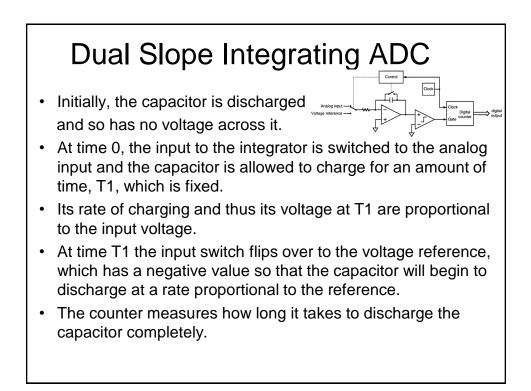

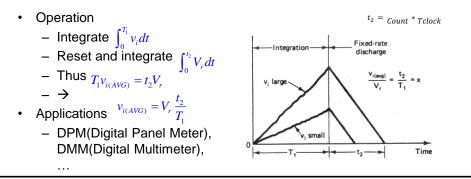

- If the capacitor is of high quality, the ratio of the discharge time to the charge time is proportional to the ratio of the input voltage to the voltage reference, and so the counter output represents the analog input voltage.

An elaboration of the dual-slope ADC is the *multislope*.

- An elaboration of the dual-slope ADC is the *multislope* integrating ADC. It achieves even higher resolution than the dual-slope ADC by discharging the capacitor at several progressively slower rates. At each rate, the counter is able to resolve finer increments of accumulated charge.

- Integrating converters do not sample the voltage itself; they *average* the voltage over the integration period and *then* they sample the average that is accumulated on the capacitor.

- This tends to reject noise that conventional sampling cannot, especially periodic noises. Most integrating ADCs operate with an integration period that is a multiple of one AC line period (1/60 or 1/50 s) so that any potential interference from stray electric or magnetic fields caused by the power system is canceled.

- Low speed

- High resolution and low cost

- Very stable

- Excellent Noise Rejection

- High frequency noise cancelled out b

- Proper T<sub>1</sub> eliminates line noise

- Easy to obtain good resolution

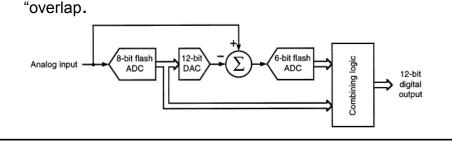

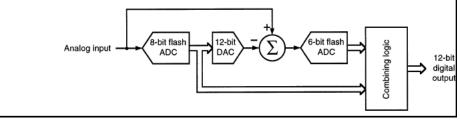

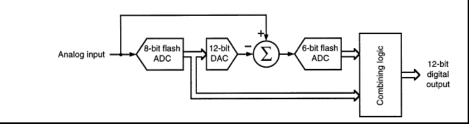

- To achieve higher sample rates than SAR ADCs at resolutions of 10 to 16 bits, *multistage* ADCs (sometimes called *subranging* or *multipass* ADCs) use the iterative approach of SAR ADCs but reduce the number of iterations in a conversion.

- Instead of using just a comparator, the multistage ADC uses low-resolution flash converters (4 to 8 bits) as building blocks.

- An example of a 12-bit two-stage ADC built out of two flash ADCs and a fast DAC.

- The 6-bit flash ADC converts the residual error of the 8-bit flash ADC. The two digital outputs are combined to produce a 12-bit conversion result.

- If each flash ADC has a T/H at its input, then each stage can be converting the residual error from the previous stage while the previous stage is converting the next sample.

- The whole converter then can effectively operate at the sample rate of the slowest stage.

- Without the extra T/Hs, a new conversion cannot start until the residues have propagated through all the stages. This variation of the multistage ADC is called a *pipelined* ADC.

- The 8-bit flash ADC takes a first "guess" at the input signal and the 6-bit flash ADC converts the error in the guess, called the "residue."

- The 12-bit DAC actually needs to have only 8 bits, but it must be accurate to 12 bits.

• If the 8-bit flash ADC were perfect, the second flash ADC would only need 4 bits. But since the first flash actually may have some error, the second flash has 2 bits of